Meanwhile, the 'on' transistors biased as followers will go to the Vgs threshold voltage, but no further. The 'off' FETs behave as a high value resistors to the ones that are 'on', behaving as source followers. The reason for there to be any voltage at all is that even when 'off', the FET still has leakage. (In this sim, Vgs threshold is set to 700mV.) You'll see the transistors in one of two states: completely 'off', or biased in the linear region at the threshold voltage. Look at the sim and mouse-over each transistor in the 'wrong' circuit, noting what Vgs is doing.

If I may ask so stupidly: pMOS is connected to the ground, on the input there is 0V, and the source is "disconnected" (since the nMOS will act as open switch), how come there is "magically" 1.0V at the output? In the case of pMOS transistors, if the input is 0V, they should be "on" and act like "closed switch", so that means there will be path from C to the ground. Why I don't really understand is that, when the both inputs A and B are at 0 volts, how come the output is 1.0 volts? If the input is 0V, then both nMOS transistors connected in parallel in the upper part of the diagram will be in the "off" state, meaning that they will behave like an "open switch". I'm not even sure if this is the correct interpretation, but so far the book provided only this kind of abstraction as "closed" or "open" switch. That is, the nMOS transistors connected in parallel act like a "closed" switch and they will be "on", but because of the "transmission voltage", the output at C will be 1.2V (from the source) - 0.5V (the "voltage drop") = 0.7V. I guess I could imagine, that there is something like "voltage drop" in the case when either or both of the inputs A, B are 1.2 volts. To derive the DC transfer characteristics for the CMOS inverter, which depicts the variation of the output voltage $(V_$ = 0.I'm currently reading through Introduction to Computing Systems: From Bits & Gates to C & Beyond and I'm a bit confused about the outputs of this OR gate (which is not an OR gate): Thus, the devices do not suffer from anybody effect. The source and the substrate (body) of the p -device is tied to the VDD rail, while the source and the substrate of the n-device are connected to the ground bus.

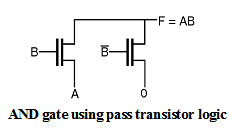

#CMOS TRANSISTOR DIAGRAM SERIES#

A complementary CMOS inverter is implemented as the series connection of a p-device and an n-device, as shown in the Figure above.

0 kommentar(er)

0 kommentar(er)